Research

| (60 intermediate revisions by one user not shown) | |||

| Line 1: | Line 1: | ||

| − | + | We aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. Our objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine. | |

<div style="float:center; font-size:110%; font-weight:bold; clear:both; padding:0; margin:0.0em;">__TOC__</div> | <div style="float:center; font-size:110%; font-weight:bold; clear:both; padding:0; margin:0.0em;">__TOC__</div> | ||

| Line 7: | Line 7: | ||

|- | |- | ||

| colspan="2" style="background:#8FBCCF; text-align:center; padding:1px; border-bottom:1px #8FBCCF solid;" | | | colspan="2" style="background:#8FBCCF; text-align:center; padding:1px; border-bottom:1px #8FBCCF solid;" | | ||

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Logic Synthesis </h2> |

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

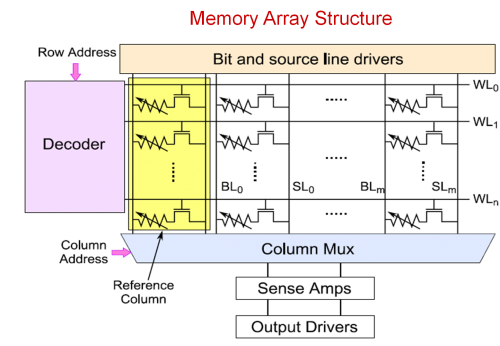

We study '''implementation of Boolean functions''' with nano-crossbar arrays where each crosspoint behaves as a diode, a FET, and a four-terminal switch. For these three types, we give array size formulations for a given Boolean function. Additionally, we focus on four-terminal switch based implementations and propose an algorithm that implements Boolean functions with '''optimal array sizes'''. | We study '''implementation of Boolean functions''' with nano-crossbar arrays where each crosspoint behaves as a diode, a FET, and a four-terminal switch. For these three types, we give array size formulations for a given Boolean function. Additionally, we focus on four-terminal switch based implementations and propose an algorithm that implements Boolean functions with '''optimal array sizes'''. | ||

| − | + | [[Image:nanoarray_logic_synthesis.png|center|none|800px|link=]] | |

| − | + | ||

| − | + | ||

| − | |||

<!-- [[Image:Research-2.png|center|none|800px|link=]] --> | <!-- [[Image:Research-2.png|center|none|800px|link=]] --> | ||

| Line 42: | Line 32: | ||

{| style="border:1px solid #abd5f5; background:#f1f5fc;" | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| | | | ||

| − | {| | + | {| |

|- valign=top | |- valign=top | ||

| width="100" |'''title''': | | width="100" |'''title''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Bernasconi_EtAl_Synthesis_on_Switching_Lattices_D_Reducible.pdf | Synthesis on Switching Lattices of Dimension-Reducible Boolean Functions]] |

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | | + | | Anna Bernasconi, Valentina Ciriani, Luca Frontini, and Gabriella Trucco |

| − | + | |- valign=top | |

| − | + | ||

| − | + | ||

| − | |- valign= | + | |

| '''presented at''': | | '''presented at''': | ||

| − | | [http:// | + | | width="450"| [http://ati.ttu.ee/vlsi-soc2016/ International Conference on Very Large Scale Integration (VLSI-SoC)], Tallinn, Estonia, 2016 |

|} | |} | ||

| − | | align=center width="70" | | + | |

| + | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www. | + | [[File:PDF.png|65px|link=http://www.nanoxcomp.itu.edu.tr/images/d/d5/Bernasconi_EtAl_Synthesis_on_Switching_Lattices_D_Reducible.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Bernasconi_EtAl_Synthesis_on_Switching_Lattices_D_Reducible.pdf | Paper]] |

| − | | align="center" width="70" | | + | | align="center" width="70" | |

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File: | + | [[File:PDF.png|65px|link=http://www.nanoxcomp.itu.edu.tr/images/a/a2/Bernasconi_EtAl_Synthesis_on_Switching_Lattices_D_Reducible_SLIDES.pdf]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [[Media:Bernasconi_EtAl_Synthesis_on_Switching_Lattices_D_Reducible_SLIDES.pdf | Slides]] |

| + | |||

|} | |} | ||

| Line 79: | Line 69: | ||

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | Dan Alexandrescu, | + | | width="450"| Dan Alexandrescu, Mustafa Altun, Lorena Anghel, Anna Bernasconi, Valentina Ciriani, and Mehdi Tahoori |

|- valign=top | |- valign=top | ||

| − | | ''' | + | | '''presented at''': |

| − | | [http://dsd-seaa2016.cs.ucy.ac.cy/index.php Euromicro Conference on Digital System Design (DSD)], | + | | width="450"| [http://dsd-seaa2016.cs.ucy.ac.cy/index.php Euromicro Conference on Digital System Design (DSD)], Limassol, Cyprus, 2016. |

|} | |} | ||

| Line 93: | Line 83: | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File: | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/7/7f/Altun_EtAl_Synthesis_and_Performance_Optimization_of_a_Switching_Nano-crossbar_Computer_SLIDES.pdf]] |

</span> | </span> | ||

| − | <br> | + | <br> [[Media:Altun_EtAl_Synthesis_and_Performance_Optimization_of_a_Switching_Nano-crossbar_Computer_SLIDES.pdf | Slides]] |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|} | |} | ||

| Line 138: | Line 98: | ||

|- valign=top | |- valign=top | ||

| − | | width="696" |''' | + | | width="696" |'''Developed Tools''' |

|} | |} | ||

{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| | | | ||

| − | {| | + | {| |

| + | |- valign=top | ||

| + | | width="100" |'''title''': | ||

| + | | width="524"|[[Media:Morgul_Altun_Optimal_Synthesis_Tools.zip | Optimal Synthesis Tool]] | ||

|- valign="top" | |- valign="top" | ||

| − | + | | '''authors''': | |

| − | | | + | | Ceylan Morgul and Mustafa Altun |

|- valign="top" | |- valign="top" | ||

| − | | ''' | + | | '''description''': |

| − | | [http:// | + | | width="524"| Two optimal synthesis tools Tool-1 and Tool-2 are developed in Matlab and Python, respectively. Both tools aim to synthesize a given target Boolean functions with an optimal size of four-terminal switch based arrays . |

| − | + | |} | |

| − | + | | align=center width="70" | | |

| − | + | <span class="plainlinks"> | |

| − | | | + | [[File:ZIP.png|65px|link=http://www.nanoxcomp.itu.edu.tr/images/b/b3/Morgul_Altun_Optimal_Synthesis_Tools.zip]]</span> |

| − | + | <br> | |

| − | + | [[Media:Morgul_Altun_Optimal_Synthesis_Tools.zip | Tool]] | |

|} | |} | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|} | |} | ||

| − | |||

| − | |||

|} | |} | ||

| Line 188: | Line 133: | ||

|- | |- | ||

| colspan="2" style="background:#8FBCBF; text-align:center; padding:1px; border-bottom:1px #8FBCBF solid;" | | | colspan="2" style="background:#8FBCBF; text-align:center; padding:1px; border-bottom:1px #8FBCBF solid;" | | ||

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Fault Tolerance </h2> |

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

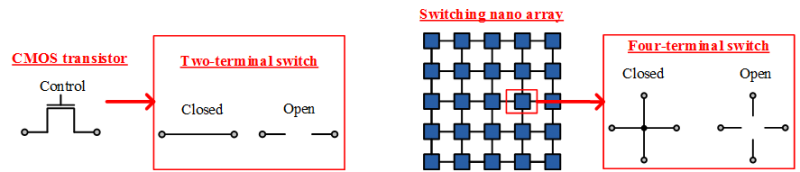

| − | + | We examine reconfigurable crossbar arrays by considering randomly occurred '''stuck-open and stuck-closed crosspoint faults'''. In the presence of '''permanent''' faults, a fast and accurate heuristic algorithm is proposed that uses the techniques of index sorting, backtracking, and row matching. In the presence of '''transient''' faults, tolerance analysis is performed by formally and recursively determining tolerable fault positions | |

| − | + | Since '''density''' feature of crossbar architectures is the main attracting point, we perform a detailed yield analysis by considering both uniform and non-uniform defect distributions. | |

| − | + | We formalize an approximate successful mapping probability metric for uniform distributions | |

| − | + | and determine '''area overheads'''. | |

| − | + | [[Image:nanoarray_fault_tolerance.png|center|none|500px|link=]] | |

| − | |||

<!-- [[Image:Research-4.png|center|none|800px|link=]] --> | <!-- [[Image:Research-4.png|center|none|800px|link=]] --> | ||

| Line 215: | Line 159: | ||

| width="696" |'''Selected Publications''' | | width="696" |'''Selected Publications''' | ||

|} | |} | ||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''title''': | ||

| + | | width="524"|[[Media:Tunali_Altun_Permanent_and_Transient_Fault_Tolerance_for_Reconfigurable_Nano-Crossbar_Arrays.pdf | Permanent and Transient Fault Tolerance for Reconfigurable Nano-Crossbar Arrays]] | ||

| + | |- valign="top" | ||

| + | | '''authors''': | ||

| + | | Onur Tunali and Mustafa Altun | ||

| + | |- valign="top" | ||

| + | | '''appeared in''': | ||

| + | | width="524" | [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=43 IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems], Vol. 36, Issue 5, pp. 747–760, 2017. | ||

| + | |} | ||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/c/cc/Tunali_Altun_Permanent_and_Transient_Fault_Tolerance_for_Reconfigurable_Nano-Crossbar_Arrays.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Tunali_Altun_Permanent_and_Transient_Fault_Tolerance_for_Reconfigurable_Nano-Crossbar_Arrays.pdf | Paper]] | ||

| + | |} | ||

| + | |||

{| style="border:1px solid #abd5f5; background:#f1f5fc;" | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| Line 221: | Line 185: | ||

|- valign=top | |- valign=top | ||

| width="100" |'''title''': | | width="100" |'''title''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Tunali_Altun_Nano_Crossbar_Yield_Analysis.pdf| Yield Analysis of Nano-Crossbar Arrays for Uniform and Clustered Defect Distributions]] |

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | | + | | Onur Tunali and [[Mustafa Altun]] |

| − | + | ||

| − | + | ||

| − | + | ||

|- valign="top" | |- valign="top" | ||

| − | | ''' | + | | '''accepted at''': |

| − | | [http:// | + | | width="450"| [http://icecs2017.org/ IEEE International Conference on Electronics Circuits and Systems (ICECS)], Batumi, Georgia, 2017. |

|} | |} | ||

| align=center width="70" | | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/6/6b/Tunali_Altun_Nano_Crossbar_Yield_Analysis.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Tunali_Altun_Nano_Crossbar_Yield_Analysis.pdf | Paper]] |

| align="center" width="70" | | | align="center" width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link= | + | [[File:PPT.jpg|60px|link=]] |

</span> | </span> | ||

| − | <br> | + | <br> Slides |

|} | |} | ||

| Line 257: | Line 218: | ||

|- valign=top | |- valign=top | ||

| − | | width="696" |''' | + | | width="696" |'''Developed Tools''' |

|} | |} | ||

{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| | | | ||

| − | {| | + | {| |

| + | |- valign=top | ||

| + | | width="100" |'''title''': | ||

| + | | width="524"|[[Media:Tunali_Altun_Fault_Tolerant_Logic_Mapping_Tool.zip | Fault Tolerant Logic Mapping Tool]] | ||

|- valign="top" | |- valign="top" | ||

| − | + | | '''authors''': | |

| − | | | + | | Onur Tunali and Mustafa Altun |

|- valign="top" | |- valign="top" | ||

| − | | ''' | + | | '''description''': |

| − | | | + | | width="524"| The tool is developed in Matlab. It aims to map logic funtions into fault crossbars such that each crosspoint has an independent fault probability up to 20%. |

| − | + | ||

| − | | | + | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|} | |} | ||

| − | + | | align=center width="70" | | |

| + | <span class="plainlinks"> | ||

| + | [[File:ZIP.png|65px|link=http://www.nanoxcomp.itu.edu.tr/images/1/16/Tunali_Altun_Fault_Tolerant_Logic_Mapping_Tool.zip]]</span> | ||

| + | <br> | ||

| + | [[Media:Tunali_Altun_Fault_Tolerant_Logic_Mapping_Tool.zip | Tool]] | ||

|} | |} | ||

| + | |||

{| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;" | ||

| | | | ||

| − | {| | + | {| |

|- valign=top | |- valign=top | ||

| − | | width=" | + | | width="100" |'''title''': |

| − | | width=" | + | | width="524"|[[Media:Tunali_Altun_Yield_Analysis_Tool.zip | Yield Analysis Tool]] |

|- valign="top" | |- valign="top" | ||

| − | | ''' | + | | '''authors''': |

| − | | | + | | Onur Tunali and Mustafa Altun |

|- valign="top" | |- valign="top" | ||

| − | | ''' | + | | '''description''': |

| − | | | + | | width="524"| The tool is developed in Matlab. This tool calculates the required crossbar size in advance according to a given logic function and a defect rate. Tool accepts two parameters, logic function file and defect rate as inputs and returns the size of crossbar. |

|} | |} | ||

| − | + | | align=center width="70" | | |

| + | <span class="plainlinks"> | ||

| + | [[File:ZIP.png|65px|link=http://www.nanoxcomp.itu.edu.tr/images/1/15/Tunali_Altun_Yield_Analysis_Tool.zip]]</span> | ||

| + | <br> | ||

| + | [[Media:Tunali_Altun_Yield_Analysis_Tool.zip | Tool]] | ||

|} | |} | ||

|} | |} | ||

| + | |||

|} | |} | ||

| + | |||

|} | |} | ||

| + | |||

<!-- STOCHASTIC --> | <!-- STOCHASTIC --> | ||

| Line 304: | Line 274: | ||

|- | |- | ||

| colspan="2" style="background:#8FBCAF; text-align:center; padding:1px; border-bottom:1px #8FBCAF solid;" | | | colspan="2" style="background:#8FBCAF; text-align:center; padding:1px; border-bottom:1px #8FBCAF solid;" | | ||

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Performance Modeling and Analysis </h2> |

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

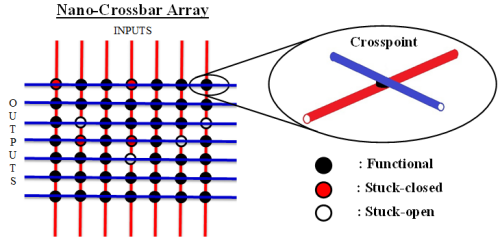

| − | + | We introduce an '''accurate capacitor-resistor model''' for nano-crossbar arrays that is to be used for '''power/delay/area''' performance analysis and optimization. In order to find capacitor and resistor values, we investigate upper/lower value limits for technology dependent parameters including doping concentration, nanowire dimension, pitch size, and layer thickness. We also use different fan-out capacitors to test the integration capability of these technologies. | |

| − | + | ||

| − | + | [[Image:nanoarray_RC_modeling.png|center|none|500px|link=]] | |

| − | |||

<!-- YAYIN --> | <!-- YAYIN --> | ||

| Line 321: | Line 289: | ||

| | | | ||

| + | |||

{| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| Line 329: | Line 298: | ||

| | | | ||

| − | {| | + | {| |

|- valign=top | |- valign=top | ||

| width="100" |'''title''': | | width="100" |'''title''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Morgul_Peker_Altun_Power-Delay-Area_Performance_Modeling_and_Analysis_for_Nano-Crossbar_Arrays.pdf | Power-Delay-Area Performance Modeling and Analysis for Nano-Crossbar Arrays]] |

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | | + | | Ceylan Morgul, Furkan Peker, and Mustafa Altun |

|- valign=top | |- valign=top | ||

| − | | ''' | + | | '''presented at''': |

| − | | [http://www.isvlsi.org/ IEEE Computer Society Annual Symposium on VLSI (ISVLSI)], | + | | width="450"| [http://www.isvlsi.org/ IEEE Computer Society Annual Symposium on VLSI (ISVLSI)], Pittsburgh, USA, 2016. |

|} | |} | ||

| − | | align=center width="70" | | + | | align=center width="70" | |

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/8/8f/Morgul_Peker_Altun_Power-Delay-Area_Performance_Modeling_and_Analysis_for_Nano-Crossbar_Arrays.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Morgul_Peker_Altun_Power-Delay-Area_Performance_Modeling_and_Analysis_for_Nano-Crossbar_Arrays.pdf | Paper]] |

| − | | align="center" width="70" | | + | | align="center" width="70" | |

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/5/5a/Morgul_Peker_Altun_Power-Delay-Area_Performance_Modeling_and_Analysis_for_Nano-Crossbar_Arrays.pptx]] |

</span> | </span> | ||

| − | <br> [http://www.ecc.itu.edu.tr/images/ | + | <br> [http://www.ecc.itu.edu.tr/images/5/5a/Morgul_Peker_Altun_Power-Delay-Area_Performance_Modeling_and_Analysis_for_Nano-Crossbar_Arrays.pptx Poster] |

| + | |} | ||

|} | |} | ||

| style="border:1px solid transparent;" | | | style="border:1px solid transparent;" | | ||

<!-- PROJE --> | <!-- PROJE --> | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|} | |} | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:#8FBC9F; text-align:center; padding:1px; border-bottom:1px # | + | | colspan="2" style="background:#8FBC9F; text-align:center; padding:1px; border-bottom:1px #8FBCAF solid;" | |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Technology Development and Performance Optimization </h2> |

| + | |||

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| − | + | Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures. Computing with crossbar arrays is achieved by its crosspoints behaving as switches, either two-terminal or four-terminal. Depending on the technology used, a two-terminal switch behaves as a diode, a resistive/memristive switch, or a field effect transistor (FET). On the other hand, a four-terminal switch has a unique behavior. While there have been many different technologies proposed for two-terminal switch based arrays, technology development for four-terminal switch based arrays, called switching lattices, has recently started. | |

| − | [[Image: | + | For both two-terminal and four-terminal switch based arrays, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. We also aim to develeop CMOS-compatible technologies for crossbar arrays, specifically for switching lattices. |

| + | |||

| + | [[Image:Research_nano-2019.png|center|none|800px|link=]] | ||

<h3> | <h3> | ||

| − | + | Technology Development</h3> | |

| − | + | Although a four-terminal switch based array offers a '''significant area advantage''', in terms of the number of switches, compared to the ones having two-terminal switches, its realization at the technology level needs | |

| + | further justifications and raises a number of questions about its | ||

| + | feasibility. We answer these questions. First, by using | ||

| + | three dimensional technology computer-aided design (TCAD) | ||

| + | simulations, we show that '''four-terminal switches can be directly implemented with the CMOS technology'''. For this purpose, we | ||

| + | try different semiconductor gate materials in different formations | ||

| + | of geometric shapes. Then, by fitting the TCAD simulation data | ||

| + | to the standard CMOS current-voltage equations, we develop a | ||

| + | Spice model of a four-terminal switch. Finally, we successfully | ||

| + | perform '''Spice circuit simulations on four-terminal switches''' with | ||

| + | different sizes. | ||

| + | [[Image:research_lattice_technology.png|center|none|800px|link=]] | ||

<h3> | <h3> | ||

| − | + | Performance Optimization</h3> | |

| − | We | + | We study crossbar arrays including the memristive ones. We |

| − | + | propose a '''defect-tolerant logic synthesis algorithms by considering area, delay, and power costs''' of the arrays. | |

| − | < | + | <!-- [[Image:Research-2.png|center|none|800px|link=]] --> |

| − | + | ||

| − | |||

<!-- YAYIN --> | <!-- YAYIN --> | ||

| Line 438: | Line 388: | ||

|- valign=top | |- valign=top | ||

| width="100" |'''title''': | | width="100" |'''title''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media: Safaltin_EtAl_Technology_Development_for_Switching_Lattices.pdf| Realization of Four-Terminal Switching Lattices: Technology Development and Circuit Modeling]] |

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | [[Mustafa Altun]] | + | | width="450"| Serzat Safaltin, Oguz Gencer, Ceylan Morgul, Levent Aksoy, Sebahattin Gurmen, Csaba Andras Moritz, and [[Mustafa Altun]] |

| − | + | ||

| − | + | ||

| − | + | ||

|- valign=top | |- valign=top | ||

| '''presented at''': | | '''presented at''': | ||

| − | | [http:// | + | | width="450"| [http://www.date-conference.com/ Design, Automation and Test in Europe (DATE)], Florence, Italy, 2019. |

|} | |} | ||

| align=center width="70" | | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/2/2c/Safaltin_EtAl_Technology_Development_for_Switching_Lattices.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Safaltin_EtAl_Technology_Development_for_Switching_Lattices.pdf | Paper]] |

| align="center" width="70" | | | align="center" width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/7/71/Safaltin_EtAl_Technology_Development_for_Switching_Lattices.pptx]] |

</span> | </span> | ||

| − | <br> [http://www.ecc.itu.edu.tr/images/ | + | <br> [http://www.ecc.itu.edu.tr/images/7/71/Safaltin_EtAl_Technology_Development_for_Switching_Lattices.pptx Slides] |

|} | |} | ||

{| style="border:1px solid #abd5f5; background:#f1f5fc;" | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| − | |||

| | | | ||

{| | {| | ||

|- valign=top | |- valign=top | ||

| width="100" |'''title''': | | width="100" |'''title''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf | Defect Tolerant Logic Synthesis for Memristor Crossbars with Performance Evaluation]] |

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | | + | | Onur Tunali and [[Mustafa Altun]] |

| + | |- valign="top" | ||

| + | | '''appeared in''': | ||

| + | | width="450" | [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=40 IEEE Micro], Vol. 38, Issue 5, pp. 22–31, 2018. | ||

|- valign="top" | |- valign="top" | ||

| '''presented at''': | | '''presented at''': | ||

| − | | [http:// | + | | width="450"| [http://www.date-conference.com/ Design, Automation and Test in Europe (DATE)], Dresden, Germany, 2018. |

|} | |} | ||

| align=center width="70" | | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/d/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/d/db/Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Tunali_Morgul_Altun_Defect_Tolerant_Memristor_Crossbars.pdf | Paper]] |

| align="center" width="70" | | | align="center" width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/b/b8/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pptx]] |

</span> | </span> | ||

| − | <br> [http://www.ecc.itu.edu.tr/images/ | + | <br> [http://www.ecc.itu.edu.tr/images/b/b8/Tunali_Altun_Logic_Synthesis_and_Defect_Tolerance_for_Memristive_Crossbars.pptx Slides] |

|} | |} | ||

| Line 496: | Line 445: | ||

|- valign=top | |- valign=top | ||

| width="100" |'''title''': | | width="100" |'''title''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Altun_EtAl_Synthesis_and_Testing_for_Switching_Nano_Crossbar_Arrays.pdf | Logic Synthesis and Testing Techniques for Switching Nano-Crossbar Arrays]] |

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | | + | | width="450"| Dan Alexandrescu, [[Mustafa Altun]], Lorena Anghel, Anna Bernasconi, Valentina Ciriani, Luca Frontini, and Mehdi Tahoori |

| + | |- valign=top | ||

| + | | '''appeared in''': | ||

| + | | width="450" | [http://www.journals.elsevier.com/microprocessors-and-microsystems/ Microprocessors and Microsystems], Vol. 54, pp. 14–25, 2017. | ||

|- valign="top" | |- valign="top" | ||

| '''presented at''': | | '''presented at''': | ||

| − | | [http:// | + | | width="450"| [http://dsd-seaa2016.cs.ucy.ac.cy/index.php Euromicro Conference on Digital System Design (DSD)], Limassol, Cyprus, 2016. |

|} | |} | ||

| + | |||

| align=center width="70" | | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/0/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/0/0a/Altun_EtAl_Synthesis_and_Testing_for_Switching_Nano_Crossbar_Arrays.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Altun_EtAl_Synthesis_and_Testing_for_Switching_Nano_Crossbar_Arrays.pdf | Paper]] |

| align="center" width="70" | | | align="center" width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File: | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/7/7f/Altun_EtAl_Synthesis_and_Performance_Optimization_of_a_Switching_Nano-crossbar_Computer_SLIDES.pdf]] |

</span> | </span> | ||

| − | <br> [ | + | <br> [[Media:Altun_EtAl_Synthesis_and_Performance_Optimization_of_a_Switching_Nano-crossbar_Computer_SLIDES.pdf | Slides]] |

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | <!-- | |

| − | + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | {| style=" | + | |

| | | | ||

{| | {| | ||

|- valign=top | |- valign=top | ||

| − | | width=" | + | | width="100" |'''title''': |

| − | | width=" | + | | width="450"|[[Media:Altun_Riedel_Logic_Synthesis_for_Switching_Lattices.pdf | Logic Synthesis for Switching Lattices]] |

|- valign="top" | |- valign="top" | ||

| − | | ''' | + | | '''authors''': |

| − | | [ | + | | [[Mustafa Altun]] and Marc Riedel |

|- valign="top" | |- valign="top" | ||

| − | | ''' | + | | '''appeared in''': |

| − | | | + | | width="450"| [http://www.computer.org/portal/web/tc IEEE Transactions on Computers], Vol. 61, Issue 11, pp. 1588–1600, 2012. |

|- valign="top" | |- valign="top" | ||

| − | | ''' | + | | '''presented at''': |

| − | | | + | | [http://www.dac.com Design Automation Conference (DAC)], Anaheim, USA, 2010. |

| − | + | ||

| − | + | ||

|} | |} | ||

| − | + | | align=center width="70" | | |

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/c/ca/Altun_Riedel_Logic_Synthesis_for_Switching_Lattices.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Altun_Riedel_Logic_Synthesis_for_Switching_Lattices.pdf | Paper]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| − | | | + | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/2/28/Altun_Riedel_Lattice-Based_Computation_of_Boolean_Functions.ppt]] |

| − | + | </span> | |

| − | + | <br> [http://www.ecc.itu.edu.tr/images/2/28/Altun_Riedel_Lattice-Based_Computation_of_Boolean_Functions.ppt Slides] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|} | |} | ||

| − | + | --> | |

|} | |} | ||

| + | | style="border:1px solid transparent;" | | ||

| + | <!-- PROJE --> | ||

| + | |||

| − | |||

|} | |} | ||

|} | |} | ||

| − | |||

| − | |||

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:#8FBC8F; text-align:center; padding:1px; border-bottom:1px # | + | | colspan="2" style="background:#8FBC8F; text-align:center; padding:1px; border-bottom:1px #8FBC9F solid;" | |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Complete Synthesis Methodology </h2> |

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| − | + | Due to the stochastic nature | |

| − | + | of nano-fabrication, nano arrays show different properties both | |

| − | + | in structural and physical device levels compared to conventional | |

| + | technologies. Mentioned factors introduce random characteristics | ||

| + | that need to be carefully considered by synthesis process. For instance, a competent synthesis methodology must consider basic | ||

| + | technology preference for switching elements, defect or fault rates | ||

| + | of the given nano switching array and the variation values as well | ||

| + | as their effects on performance metrics including power, delay, and | ||

| + | area. Presented synthesis methodology in this study comprehensively covers the all specified factors and provides optimization | ||

| + | algorithms for each step of the process. | ||

| + | |||

| + | |||

| + | [[Image:Research-synthesis-methodology.png|center|none|800px|link=]] | ||

| + | |||

<!-- YAYIN --> | <!-- YAYIN --> | ||

| Line 594: | Line 544: | ||

| width="696" |'''Selected Publications''' | | width="696" |'''Selected Publications''' | ||

|} | |} | ||

| + | |||

{| style="border:1px solid #abd5f5; background:#f1f5fc;" | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| Line 600: | Line 551: | ||

|- valign=top | |- valign=top | ||

| width="100" |'''title''': | | width="100" |'''title''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media: Morgul_EtAl_Integrated_Synthesis_Methodology for_Crossbar_Arrays.pdf | Integrated Synthesis Methodology for Crossbar Arrays]] |

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | | + | | width="450"| Ceylan Morgul, Luca Frontini, Onur Tunali, Ioana Vatajelu, Valentina Ciriani, Lorena Anghel, Csaba Moritz, Mircea Stan, Dan Alexandrescu, and Mustafa Altun |

| − | + | ||

| − | | | + | |

| − | + | ||

|- valign="top" | |- valign="top" | ||

| '''presented at''': | | '''presented at''': | ||

| − | | [http://www. | + | | width="450"|[http://www.nanoarch.org/ IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH)], Athens, Greece, 2018. |

|} | |} | ||

| + | |||

| align=center width="70" | | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/b/b1/Morgul_EtAl_Integrated_Synthesis_Methodology_for_Crossbar_Arrays.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media: Morgul_EtAl_Integrated_Synthesis_Methodology_for_Crossbar_Arrays.pdf | Paper]] |

| align="center" width="70" | | | align="center" width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/ | + | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/b/bd/Morgul_EtAl_Integrated_Synthesis_Methodology_for_Crossbar_Arrays.pptx]] |

</span> | </span> | ||

| − | <br> [http://www.ecc.itu.edu.tr/images/ | + | <br> [http://www.ecc.itu.edu.tr/images/b/bd/Morgul_EtAl_Integrated_Synthesis_Methodology_for_Crossbar_Arrays.pptx Slides] |

|} | |} | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

|- | |- | ||

| − | | colspan="2" style="background:#8FBC7F; text-align:center; padding:1px; border-bottom:1px # | + | | colspan="2" style="background:#8FBC7F; text-align:center; padding:1px; border-bottom:1px #8FBC8F solid;" | |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> | + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Crossbar Memories </h2> |

|- | |- | ||

| valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

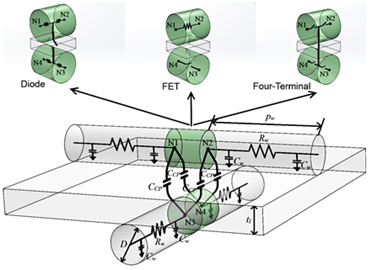

| − | + | In this work, we investigated the sensing challenges of spin-transfer torque MRAMs structured as nano-crossbar memories. To overcome | |

| − | + | the problems of reading this type of memory, we have proposed a voltage sensing amplifier topology and compared its | |

| + | performance to that of the current sensing amplifier in terms of power, speed, and bit error rate performance. | ||

| + | |||

| + | [[Image:Crossbar-memory.png|center|none|500px|link=]] | ||

| − | |||

<!-- YAYIN --> | <!-- YAYIN --> | ||

{| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | ||

| Line 663: | Line 607: | ||

|- valign=top | |- valign=top | ||

| width="100" |'''title''': | | width="100" |'''title''': | ||

| − | | width="450"|[[Media: | + | | width="450"|[[Media:Atasoyu_Altun_Ozoguz_Sensing_Schemes_for_STT-MRAMs.pdf | Sensing Schemes for STT-MRAMs structured with high TMR in low RA MTJs]] |

|- valign="top" | |- valign="top" | ||

| '''authors''': | | '''authors''': | ||

| − | | | + | | Mesut Atasoyu, Mustafa Altun, Serdar Ozoguz, and Kaushik Roy |

|- valign="top" | |- valign="top" | ||

| − | | '''appeared in''': | + | | '''appeared in''': |

| − | | [http://www. | + | | width="450"| [http://www.journals.elsevier.com/microelectronics-journal Microelectronics Journal], accepted for publication, 2019. |

| + | |- valign="top" | ||

| + | | '''presented at''': | ||

| + | | width="450"| [http://smacd2017.unisa.it/ International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD)], Taormina, Italy, 2017. | ||

|} | |} | ||

| align=center width="70" | | | align=center width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PDF.png|65px|link=http://www. | + | [[File:PDF.png|65px|link=http://www.nanoxcomp.itu.edu.tr/images/a/af/Atasoyu_Altun_Ozoguz_Sensing_Schemes_for_STT-MRAMs.pdf]]</span> |

<br> | <br> | ||

| − | [[Media: | + | [[Media:Atasoyu_Altun_Ozoguz_Sensing_Schemes_for_STT-MRAMs.pdf | Paper]] |

| align="center" width="70" | | | align="center" width="70" | | ||

<span class="plainlinks"> | <span class="plainlinks"> | ||

| − | [[File:PPT.jpg|60px|link=http://www. | + | [[File:PPT.jpg|60px|link=http://www.nanoxcomp.itu.edu.tr/images/7/7a/Atasoyu_EtAl_Spin-Torque_Memristor_based_Offset_Cancellation.pptx]] |

</span> | </span> | ||

| − | <br> [http://www. | + | <br> [http://www.nanoxcomp.itu.edu.tr/images/7/7a/Atasoyu_EtAl_Spin-Torque_Memristor_based_Offset_Cancellation.pptx Slides] |

|} | |} | ||

Latest revision as of 18:00, 13 May 2019

We aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. Our objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine.

Contents |

Logic Synthesis | |||||||||||||||||||||||||||||||||

|

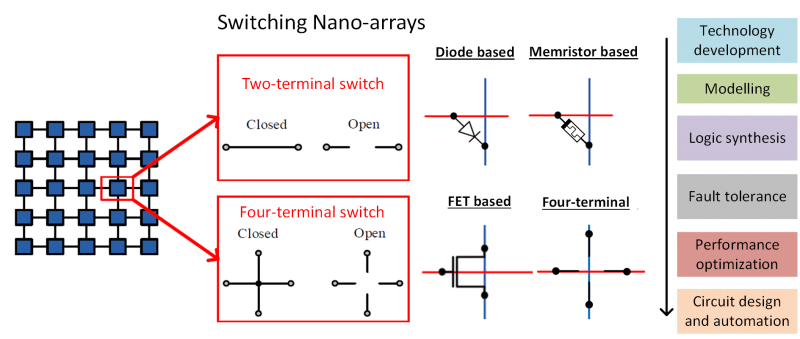

We study implementation of Boolean functions with nano-crossbar arrays where each crosspoint behaves as a diode, a FET, and a four-terminal switch. For these three types, we give array size formulations for a given Boolean function. Additionally, we focus on four-terminal switch based implementations and propose an algorithm that implements Boolean functions with optimal array sizes.

| |||||||||||||||||||||||||||||||||

Fault Tolerance | ||||||||||||||||||||||||||||||||||||||||

|

We examine reconfigurable crossbar arrays by considering randomly occurred stuck-open and stuck-closed crosspoint faults. In the presence of permanent faults, a fast and accurate heuristic algorithm is proposed that uses the techniques of index sorting, backtracking, and row matching. In the presence of transient faults, tolerance analysis is performed by formally and recursively determining tolerable fault positions Since density feature of crossbar architectures is the main attracting point, we perform a detailed yield analysis by considering both uniform and non-uniform defect distributions. We formalize an approximate successful mapping probability metric for uniform distributions and determine area overheads.

| ||||||||||||||||||||||||||||||||||||||||

Performance Modeling and Analysis | |||||||||||||

|

We introduce an accurate capacitor-resistor model for nano-crossbar arrays that is to be used for power/delay/area performance analysis and optimization. In order to find capacitor and resistor values, we investigate upper/lower value limits for technology dependent parameters including doping concentration, nanowire dimension, pitch size, and layer thickness. We also use different fan-out capacitors to test the integration capability of these technologies.

| |||||||||||||

Technology Development and Performance Optimization | |||||||||||||||||||||||||||||||||||

|

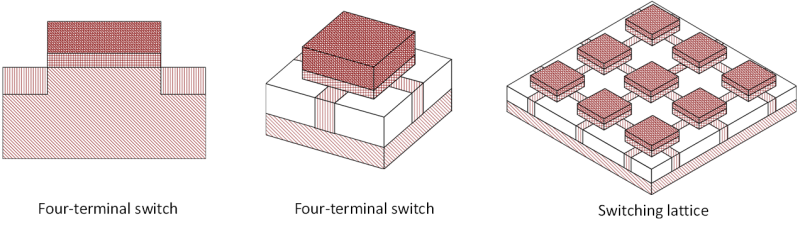

Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures. Computing with crossbar arrays is achieved by its crosspoints behaving as switches, either two-terminal or four-terminal. Depending on the technology used, a two-terminal switch behaves as a diode, a resistive/memristive switch, or a field effect transistor (FET). On the other hand, a four-terminal switch has a unique behavior. While there have been many different technologies proposed for two-terminal switch based arrays, technology development for four-terminal switch based arrays, called switching lattices, has recently started. For both two-terminal and four-terminal switch based arrays, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. We also aim to develeop CMOS-compatible technologies for crossbar arrays, specifically for switching lattices.  Technology DevelopmentAlthough a four-terminal switch based array offers a significant area advantage, in terms of the number of switches, compared to the ones having two-terminal switches, its realization at the technology level needs further justifications and raises a number of questions about its feasibility. We answer these questions. First, by using three dimensional technology computer-aided design (TCAD) simulations, we show that four-terminal switches can be directly implemented with the CMOS technology. For this purpose, we try different semiconductor gate materials in different formations of geometric shapes. Then, by fitting the TCAD simulation data to the standard CMOS current-voltage equations, we develop a Spice model of a four-terminal switch. Finally, we successfully perform Spice circuit simulations on four-terminal switches with different sizes.  Performance OptimizationWe study crossbar arrays including the memristive ones. We propose a defect-tolerant logic synthesis algorithms by considering area, delay, and power costs of the arrays.

| |||||||||||||||||||||||||||||||||||

Complete Synthesis Methodology | ||||||||||||||||||||||||||||||

|

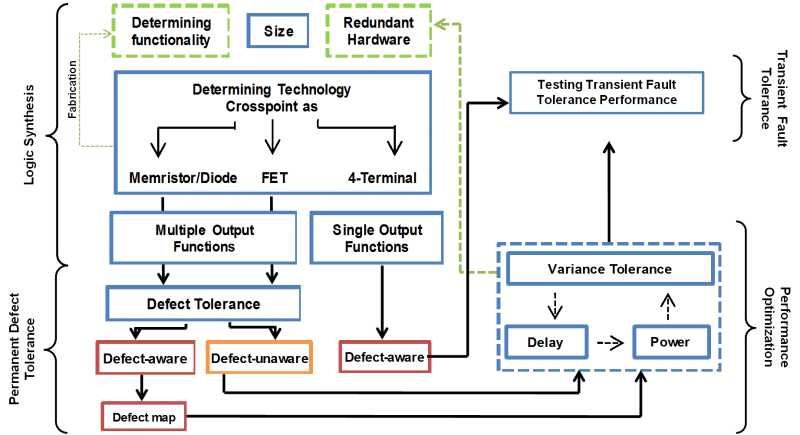

Due to the stochastic nature of nano-fabrication, nano arrays show different properties both in structural and physical device levels compared to conventional technologies. Mentioned factors introduce random characteristics that need to be carefully considered by synthesis process. For instance, a competent synthesis methodology must consider basic technology preference for switching elements, defect or fault rates of the given nano switching array and the variation values as well as their effects on performance metrics including power, delay, and area. Presented synthesis methodology in this study comprehensively covers the all specified factors and provides optimization algorithms for each step of the process.

|

||||||||||||||||||||||||||||||