Main Page

From NANOxCOMP H2020 Project

Welcome to the NANOxCOMP Project

|

|

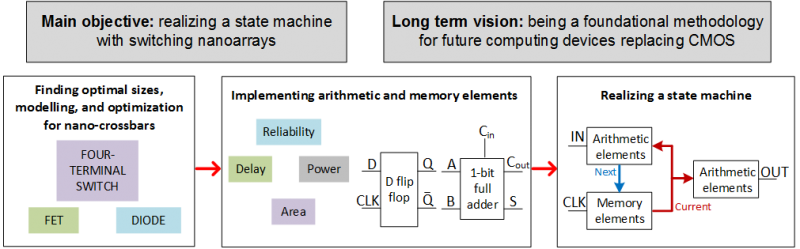

Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures, and fabricated by exploiting self-assembly as opposed to purely using lithography based conventional and relatively costly CMOS fabrication techniques. Currently, nano-crossbar arrays are fabricated such that each crosspoint can be used as a conventional electronic component such as a diode, a FET, or a switch. This is a unique opportunity that allows us to integrate well developed conventional circuit design techniques into nano-crossbar arrays. Motivated by this, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer.

Project objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine.

|

Project details

| title:

|

Synthesis and Performance Optimization of a Switching Nano-Crossbar Computer

|

| acronym:

|

NANOxCOMP

|

| principal investigator / coordinator:

|

Mustafa Altun, ECC Group, Istanbul Technical University

|

| partner(s):

|

- Dr. Dan Alexandrescu, IROC Techonogies, France

- Prof. Lorena Anghel, TIMA Lab., France (terminated)

- Prof. Valentina Ciriani, ALOS Lab., University of Milan, Italy.

- Prof. Csaba A. Moritz, Nanoscale Computing Fabrics Lab., University of Massachusetts, USA

- Prof. Kaushik Roy, Nanoelectronics Research Lab., Purdue University, USA

- Prof. Georgios Sirakoulis, Department of Electrical and Computer Engineering, Democritus University of Thrace, Greece (new partner)

- Prof. Mircea Stan, High-Performance Low-Power Lab., University of Virginia, USA

- Prof. Mehdi B. Tahoori, Dependable Nano-Computing Group, Karlsruhe Institute of Technology, Germany

|

| funding agency & program:

|

European Union/European Commission H2020 MSCA Research and Innovation Staff Exchange Program (RISE)

RISE Video

|

| budget:

|

724.500 EURO

|

| duration:

|

2015-2019

|

This project

- gathers globally leading research groups working on nanoelectronics and EDA;

- targets variety of emerging technologies including nanowire/nanotube crossbar arrays, magnetic switch-based structures, and crossbar memories; and

- contributes to the construction of emerging computers beyond CMOS by proposing nano-crossbar based computer architectures.

|

|

This project has received funding from the European Union's H2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 691178.

|

|

Project news

- We present our work "Analog Neural Network based on Memristor Crossbar Arrays" in ELECO 2019.

- We present our work "Noise-induced Performance Enhancement of Variability-aware Memristor Networks" in ICECS 2019.

- We give a keynote talk "Computing with Nano-crossbar Arrays" in CENICS 2019.

- We present our work "Testability of Switching Lattices in the Cellular Fault Model" in DSD 2019.

- A new partner Prof. Georgios Sirakoulis from Democritus University of Thrace, Greece has joined our consortium. Welcome!

- We present our work "Realization of Four-Terminal Switching Lattices: Technology Development and Circuit Modeling" in a premier conference on electronic design automation DATE 2019.

- We present our work "A Satisfiability-Based Approximate Algorithm for Logic Synthesis Using Switching Lattices" in a premier conference on electronic design automation DATE 2019.

- We present our work "Fault Mitigation of Switching Lattices under the Stuck-At-Fault Model" in LATS 2019.

- We present our work "Testability of Switching Lattices in the Stuck at Fault Model" in VLSI-Soc 2018.

- We present our work "Integrated Synthesis Methodology for Crossbar Arrays" in a leading conference on nanocircuits/nanoarchitectures IEEE/ACM-NANOARCH 2018.

- We present our work "Logic Synthesis and Defect Tolerance for Memristive Crossbar Arrays" in a premier conference on electronic design automation DATE 2018.

- We present our work "Yield Analysis of Nano-Crossbar Arrays for Uniform and Clustered Defect Distributions" in IEEE-ICECS 2017.

- Our two papers in the area of fault tolerance for nano-crossbar arrays are accepted in journals CSUR and TETC having impact factors of 6,8 and 3,8. This endorses our leading expertise in this area.

- We present our work "Composition of Switching Lattices and Autosymmetric Boolean Function Synthesis" in DSD 2017.

- We present our work "Spintronic Memristor based Offset Cancellation Technique for Sense Amplifiers" in SMACD 2017.

- We successfully have our midterm review meeting in Lausanne, Switzerland on March 2017. For the agenda click here.

- We present our work "Computing with Nano-Crossbar Arrays: Logic Synthesis and Fault Tolerance" in a premier conference on electronic design automation DATE 2017.

- Our paper is accepted in a leading journal in design automation IEEE TCAD.

- We present our work "Synthesis on Switching Lattices of Dimension-Reducible Boolean Functions" in VLSI-Soc 2016.

- We present our project and our work on logic synthesis of switching nanoarrays in DSD 2016.

- We present our work "Power-Delay-Area Performance Modeling and Analysis for Nano-Crossbar Arrays" in IEEE-ISVLSI 2016.

- We give an invited talk "Circuit Design and Optimization of Nano-Crossbar Arrays" in NanoTR-12.

- We give a plenary talk "Implementation of a Switching Nano-Crossbar Computer" in ACS 2016.

- We present and exhibit our EU H2020 project NANOxCOMP in a premier conference on electronic design automation DATE 2016 with over 1000 attendees from academia and industry.

|

|