Main Page

| Line 42: | Line 42: | ||

| width="500"| | | width="500"| | ||

* Dr. Dan Alexandrescu, [http://www.iroctech.com/ IROC Techonogies], France <br> | * Dr. Dan Alexandrescu, [http://www.iroctech.com/ IROC Techonogies], France <br> | ||

| − | * Prof. Lorena Anghel, [http://tima.imag.fr/tima/en/index.html TIMA Lab.], France <br> | + | * Prof. Lorena Anghel, [http://tima.imag.fr/tima/en/index.html TIMA Lab.], France (''TERMINATED'')<br> |

* Prof. Valentina Ciriani, [http://alos.di.unimi.it/ ALOS Lab., University of Milan], Italy. <br> | * Prof. Valentina Ciriani, [http://alos.di.unimi.it/ ALOS Lab., University of Milan], Italy. <br> | ||

* Prof. Csaba A. Moritz, [http://www.umass.edu/nanofabrics/ Nanoscale Computing Fabrics Lab., University of Massachusetts], USA <br> | * Prof. Csaba A. Moritz, [http://www.umass.edu/nanofabrics/ Nanoscale Computing Fabrics Lab., University of Massachusetts], USA <br> | ||

* Prof. Kaushik Roy, [http://engineering.purdue.edu/NRL/index.html Nanoelectronics Research Lab., Purdue University], USA <br> | * Prof. Kaushik Roy, [http://engineering.purdue.edu/NRL/index.html Nanoelectronics Research Lab., Purdue University], USA <br> | ||

| + | * Prof. Georgios Sirakoulis, [https://www.ee.duth.gr/en/ Department of Electrical and Computer Engineering, Democritus University of Thrace], Greece (''NEW PARTNER'') <br> | ||

* Prof. Mircea Stan, [http://hplp.ece.virginia.edu/home High-Performance Low-Power Lab., University of Virginia], USA <br> | * Prof. Mircea Stan, [http://hplp.ece.virginia.edu/home High-Performance Low-Power Lab., University of Virginia], USA <br> | ||

* Prof. Mehdi B. Tahoori, [http://cdnc.itec.kit.edu/index.php Dependable Nano-Computing Group, Karlsruhe Institute of Technology], Germany | * Prof. Mehdi B. Tahoori, [http://cdnc.itec.kit.edu/index.php Dependable Nano-Computing Group, Karlsruhe Institute of Technology], Germany | ||

Revision as of 11:57, 23 October 2019

Welcome to the NANOxCOMP Project | |

|

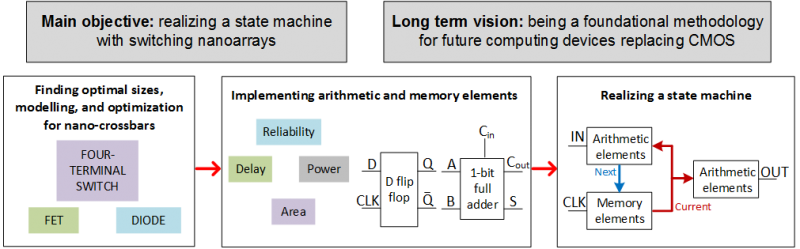

Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures, and fabricated by exploiting self-assembly as opposed to purely using lithography based conventional and relatively costly CMOS fabrication techniques. Currently, nano-crossbar arrays are fabricated such that each crosspoint can be used as a conventional electronic component such as a diode, a FET, or a switch. This is a unique opportunity that allows us to integrate well developed conventional circuit design techniques into nano-crossbar arrays. Motivated by this, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. Project objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine.

| |

This project has received funding from the European Union's H2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 691178.

|

|

|