Research

| Line 505: | Line 505: | ||

<!-- PROJE --> | <!-- PROJE --> | ||

| + | |||

| + | |} | ||

| + | |} | ||

| + | |||

| + | |||

| + | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;" | ||

| + | |- | ||

| + | | colspan="2" style="background:#8FBC8F; text-align:center; padding:1px; border-bottom:1px #8FBC9F solid;" | | ||

| + | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Reliability of Electronic Products </h2> | ||

| + | |- | ||

| + | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> | | ||

| + | |||

| + | The rapid developments in electronics, especially in the last decade, have elevated the importance of electronics reliability. Conventionally used accelerated reliability tests have lost their significance; time consuming and expensive feature of these tests is against the demands of today's very rapid electronic product cycles. In this study, we propose less costly, yet accurate, reliability prediction techniques using field return data, new accelerated test methodologies, and physics of failure based simulations. We cooperate with one of the Europe’s largest household appliance companies [http://www.arcelik.com.tr/default.aspx?lang=en-US Arçelik A.Ş.]. | ||

| + | |||

| + | [[Image:Research-3.png|center|none|800px|link=]] | ||

| + | |||

| + | <h3> | ||

| + | Reliability Analysis and Prediction with Field Data</h3> | ||

| + | |||

| + | We propose an '''accurate reliability prediction''' model for high-volume electronic products throughout their warranty periods by using field return data. Our model is constructed on a Weibull-exponential hazard rate scheme by using the '''proposed change point detection method''' based on backward and forward data analysis. Our prediction model can make a '''36-month''' (full warranty) reliability prediction of an electronic board with using its field data as short as '''3 months'''. | ||

| + | |||

| + | <h3> | ||

| + | Degradation Processes in Varistors</h3> | ||

| + | |||

| + | We investigate different degradation mechanisms of ZnO varistors. We propose a model showing how the varistor voltage Vv changes by time for different stress levels. For this purpose, accelerated degradation tests are applied for different AC current levels; then voltage values are measured. Different from the common practice in the literature that considers a degradation with only decreasing Vv values, we demonstrate '''either an increasing or a decreasing trend in the Vv parameter'''. | ||

| + | <!-- | ||

| + | <h3> | ||

| + | Calibrated Accelerated Life Testing</h3> | ||

| + | |||

| + | Dramatic decrease in failure rates for electronic products makes conventional accelerated life tests ('''ALT''') extremely time consuming and costly. Recently proposed calibrated accelerated life tests ('''CALT''') aim to use fewer samples than those used in ALT. We thoroughly compare ALT and CALT by considering the effects of failure rate, acceleration factor, and stress level on the required test time.--> | ||

| + | |||

| + | <!-- YAYIN --> | ||

| + | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;" | ||

| + | | class="MainPageBG" style="width:50%; border:0px solid #D8BFD8; vertical-align:top; color:#000;" | | ||

| + | {| id="mp-left" style="width:100%; vertical-align:top;" | ||

| + | |||

| + | | | ||

| + | |||

| + | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;" | ||

| + | |||

| + | |- valign=top | ||

| + | | width="696" |'''Selected Publications''' | ||

| + | |} | ||

| + | |||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''title''': | ||

| + | | width="450"|[[Media:Altun_Comert_A_Change-Point_based_Reliability_Prediction_Model_using_Field_Return_Data.pdf| A Change-Point based Reliability Prediction Model using Field Return Data]] | ||

| + | |- valign="top" | ||

| + | | '''authors''': | ||

| + | | [[Mustafa Altun]] and Vehbi Comert | ||

| + | |- valign=top | ||

| + | | '''appeared in''': | ||

| + | | width="450"| [http://www.journals.elsevier.com/reliability-engineering-and-system-safety Reliability Engineering and System Safety], Vol. 156, pp. 175–184, 2016. | ||

| + | |- valign=top | ||

| + | | '''presented at''': | ||

| + | | width="450"| [http://rams.org/ Reliability and Maintainability Symposium (RAMS)], Palm Harbor, USA, 2015. | ||

| + | |} | ||

| + | |||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/1/16/Altun_Comert_A_Change-Point_based_Reliability_Prediction_Model_using_Field_Return_Data.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Altun_Comert_A_Change-Point_based_Reliability_Prediction_Model_using_Field_Return_Data.pdf | Paper]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/a/a7/Comert_Altun_Nadar_Erturk_Warranty_Forecasting_of_Electronic_Boards_using_Short-term_Field_Data.pptx]] | ||

| + | </span> | ||

| + | <br> [http://www.ecc.itu.edu.tr/images/a/a7/Comert_Altun_Nadar_Erturk_Warranty_Forecasting_of_Electronic_Boards_using_Short-term_Field_Data.pptx Slides] | ||

| + | |} | ||

| + | |||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''title''': | ||

| + | | width="450"|[[Media: Yadavari_Altun_Distinct_Degradation_Processes_in_ZnO_varistors.pdf | Distinct Degradation Processes in ZnO Varistors: Reliability Analysis and Modeling with Accelerated AC Tests]] | ||

| + | |- valign="top" | ||

| + | | '''authors''': | ||

| + | | Hadi Yadavari and [[Mustafa Altun]] | ||

| + | |- valign=top | ||

| + | | '''appeared in''': | ||

| + | | width="450"| [http://journals.tubitak.gov.tr/elektrik/index.htm;jsessionid=848207EBE52EFE10C78B78C76A0FEAD9 Turkish Journal of Electrical Engineering and Computer Sciences], Vol. 25, No. 4, pp. 3240–3252, 2017. | ||

| + | |- valign="top" | ||

| + | | '''presented at''': | ||

| + | | width="450"| [http://esrel2015.ethz.ch/ European Safety and Reliability Conference (ESREL)], Zurich, Switzerland, 2015. | ||

| + | |} | ||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/d/dd/Yadavari_Altun_Distinct_Degradation_Processes_in_ZnO_varistors.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Yadavari_Altun_Distinct_Degradation_Processes_in_ZnO_varistors.pdf | Paper]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/d/de/Yadavari_EtAl_Effects_of_ZnO_Varistor_Degradation_on_the_Overvoltage_Protection_Mechanism_of_Electronic_Boards.pptx]] | ||

| + | </span> | ||

| + | <br> [http://www.ecc.itu.edu.tr/images/d/de/Yadavari_EtAl_Effects_of_ZnO_Varistor_Degradation_on_the_Overvoltage_Protection_Mechanism_of_Electronic_Boards.pptx Slides] | ||

| + | |} | ||

| + | <!-- | ||

| + | {| style="border:1px solid #abd5f5; background:#f1f5fc;" | ||

| + | |||

| + | | | ||

| + | {| | ||

| + | |- valign=top | ||

| + | | width="100" |'''title''': | ||

| + | | width="450"|[[Media:Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pdf | Extensive Investigation of Calibrated Accelerated Life Testing (CALT) in Comparison with Classical Accelerated Life Testing (ALT)]] | ||

| + | |- valign="top" | ||

| + | | '''authors''': | ||

| + | | Burak Sal and [[Mustafa Altun]] | ||

| + | |- valign="top" | ||

| + | | '''presented at''': | ||

| + | | width="450"| [http://esrel2015.ethz.ch/ European Safety and Reliability Conference (ESREL)], Zurich, Switzerland, 2015. | ||

| + | |} | ||

| + | | align=center width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/0/07/Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pdf]]</span> | ||

| + | <br> | ||

| + | [[Media:Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pdf | Paper]] | ||

| + | | align="center" width="70" | | ||

| + | <span class="plainlinks"> | ||

| + | |||

| + | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/a/a8/Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pptx]] | ||

| + | </span> | ||

| + | <br> [http://www.ecc.itu.edu.tr/images/a/a8/Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pptx Slides] | ||

| + | |} --> | ||

| + | |} | ||

|} | |} | ||

|} | |} | ||

Revision as of 15:51, 13 May 2019

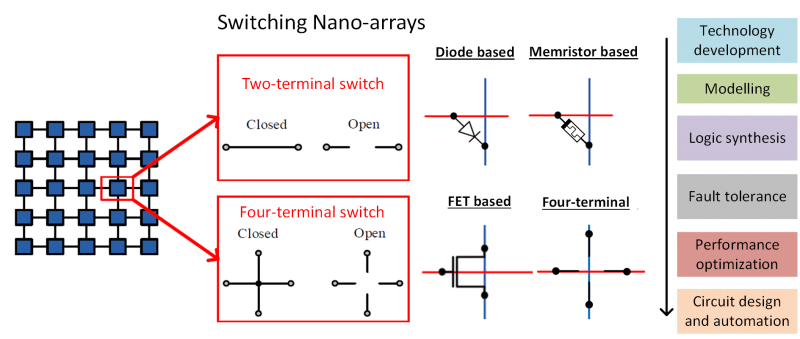

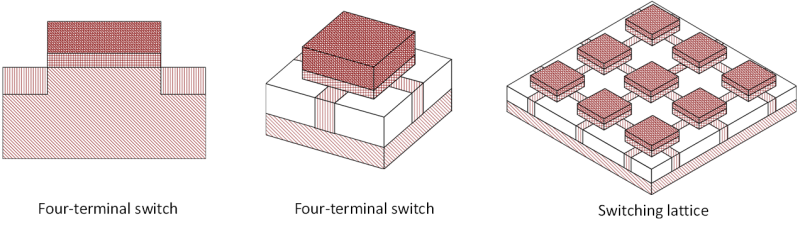

We aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. Our objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine.

Contents |

Logic Synthesis | |||||||||||||||||||||||||||||||||

|

We study implementation of Boolean functions with nano-crossbar arrays where each crosspoint behaves as a diode, a FET, and a four-terminal switch. For these three types, we give array size formulations for a given Boolean function. Additionally, we focus on four-terminal switch based implementations and propose an algorithm that implements Boolean functions with optimal array sizes.

| |||||||||||||||||||||||||||||||||

Fault Tolerance | ||||||||||||||||||||||||||||||||||||||||

|

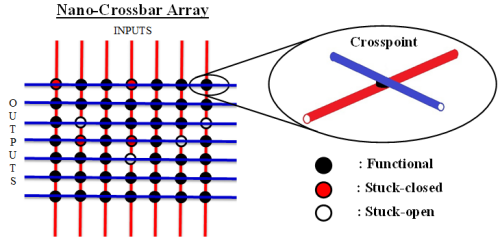

We examine reconfigurable crossbar arrays by considering randomly occurred stuck-open and stuck-closed crosspoint faults. In the presence of permanent faults, a fast and accurate heuristic algorithm is proposed that uses the techniques of index sorting, backtracking, and row matching. In the presence of transient faults, tolerance analysis is performed by formally and recursively determining tolerable fault positions Since density feature of crossbar architectures is the main attracting point, we perform a detailed yield analysis by considering both uniform and non-uniform defect distributions. We formalize an approximate successful mapping probability metric for uniform distributions and determine area overheads.

| ||||||||||||||||||||||||||||||||||||||||

Performance Modeling and Analysis | |||||||||||||

|

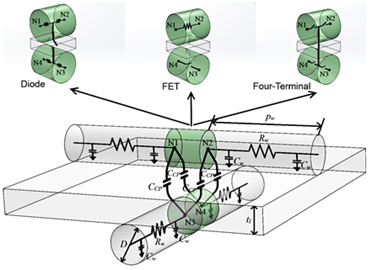

We introduce an accurate capacitor-resistor model for nano-crossbar arrays that is to be used for power/delay/area performance analysis and optimization. In order to find capacitor and resistor values, we investigate upper/lower value limits for technology dependent parameters including doping concentration, nanowire dimension, pitch size, and layer thickness. We also use different fan-out capacitors to test the integration capability of these technologies.

| |||||||||||||

Technology Development and Performance Optimization | |||||||||||||||||||||||||||||||||||

|

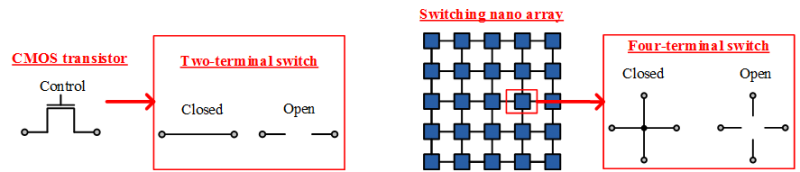

Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures. Computing with crossbar arrays is achieved by its crosspoints behaving as switches, either two-terminal or four-terminal. Depending on the technology used, a two-terminal switch behaves as a diode, a resistive/memristive switch, or a field effect transistor (FET). On the other hand, a four-terminal switch has a unique behavior. While there have been many different technologies proposed for two-terminal switch based arrays, technology development for four-terminal switch based arrays, called switching lattices, has recently started. For both two-terminal and four-terminal switch based arrays, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. We also aim to develeop CMOS-compatible technologies for crossbar arrays, specifically for switching lattices.  Technology DevelopmentAlthough a four-terminal switch based array offers a significant area advantage, in terms of the number of switches, compared to the ones having two-terminal switches, its realization at the technology level needs further justifications and raises a number of questions about its feasibility. We answer these questions. First, by using three dimensional technology computer-aided design (TCAD) simulations, we show that four-terminal switches can be directly implemented with the CMOS technology. For this purpose, we try different semiconductor gate materials in different formations of geometric shapes. Then, by fitting the TCAD simulation data to the standard CMOS current-voltage equations, we develop a Spice model of a four-terminal switch. Finally, we successfully perform Spice circuit simulations on four-terminal switches with different sizes.  Performance OptimizationWe study crossbar arrays including the memristive ones. We propose a defect-tolerant logic synthesis algorithms by considering area, delay, and power costs of the arrays.

| |||||||||||||||||||||||||||||||||||

Reliability of Electronic Products | |||||||||||||||||||||||||

|

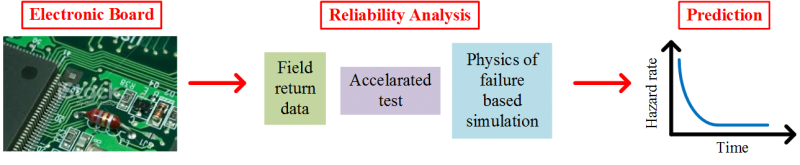

The rapid developments in electronics, especially in the last decade, have elevated the importance of electronics reliability. Conventionally used accelerated reliability tests have lost their significance; time consuming and expensive feature of these tests is against the demands of today's very rapid electronic product cycles. In this study, we propose less costly, yet accurate, reliability prediction techniques using field return data, new accelerated test methodologies, and physics of failure based simulations. We cooperate with one of the Europe’s largest household appliance companies Arçelik A.Ş..  Reliability Analysis and Prediction with Field DataWe propose an accurate reliability prediction model for high-volume electronic products throughout their warranty periods by using field return data. Our model is constructed on a Weibull-exponential hazard rate scheme by using the proposed change point detection method based on backward and forward data analysis. Our prediction model can make a 36-month (full warranty) reliability prediction of an electronic board with using its field data as short as 3 months. Degradation Processes in VaristorsWe investigate different degradation mechanisms of ZnO varistors. We propose a model showing how the varistor voltage Vv changes by time for different stress levels. For this purpose, accelerated degradation tests are applied for different AC current levels; then voltage values are measured. Different from the common practice in the literature that considers a degradation with only decreasing Vv values, we demonstrate either an increasing or a decreasing trend in the Vv parameter.

| |||||||||||||||||||||||||