Main Page

| Line 113: | Line 113: | ||

| style="padding:2px;" | <h2 id="mp-itn-h2" style="margin:3px; background:#BC8F8F; font-size:125%; font-weight:bold; border:1px solid #BA55D3; text-align:left; color:#000; padding:0.2em 0.4em;">Project news</h2> | | style="padding:2px;" | <h2 id="mp-itn-h2" style="margin:3px; background:#BC8F8F; font-size:125%; font-weight:bold; border:1px solid #BA55D3; text-align:left; color:#000; padding:0.2em 0.4em;">Project news</h2> | ||

| − | * We publicly introduce our project in [http://www.english.sci-all.com/ Science Unites All (SCI-ALL)] - [http://ec.europa.eu/research/mariecurieactions/about/researchers-night_en European | + | * We publicly introduce our project in [http://www.english.sci-all.com/ Science Unites All (SCI-ALL)] - [http://ec.europa.eu/research/mariecurieactions/about/researchers-night_en European Researchers' Night Event 2017]. |

| − | Researchers' Night Event 2017]. | + | |

* Our two papers in the area of ''fault tolerance for nano-crossbar arrays'' are accepted in journals [http://csur.acm.org/ CSUR] and [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 TETC] having impact factors of 6,8 and 3,8. This endorses our leading expertise in this area. | * Our two papers in the area of ''fault tolerance for nano-crossbar arrays'' are accepted in journals [http://csur.acm.org/ CSUR] and [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=6245516 TETC] having impact factors of 6,8 and 3,8. This endorses our leading expertise in this area. | ||

Revision as of 11:13, 19 September 2017

Welcome to the NANOxCOMP Project | |

|

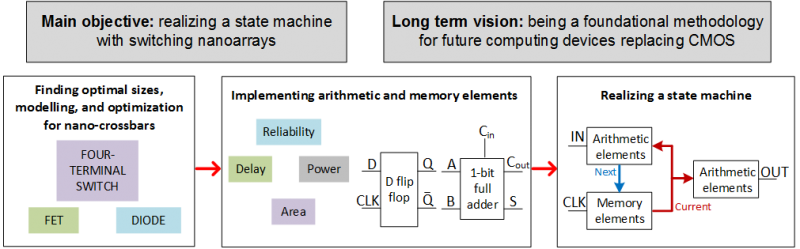

Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures, and fabricated by exploiting self-assembly as opposed to purely using lithography based conventional and relatively costly CMOS fabrication techniques. Currently, nano-crossbar arrays are fabricated such that each crosspoint can be used as a conventional electronic component such as a diode, a FET, or a switch. This is a unique opportunity that allows us to integrate well developed conventional circuit design techniques into nano-crossbar arrays. Motivated by this, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. Project objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine.

| |

This project has received funding from the European Union's H2020 research and innovation programme under the Marie Skłodowska-Curie grant agreement No 691178.

|

|

|