|

|

| Line 337: |

Line 337: |

| | |} | | |} |

| | |} | | |} |

| − | |}

| |

| − | |}

| |

| − |

| |

| − | <!-- RELIABILITY -->

| |

| − |

| |

| − | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;"

| |

| − | |-

| |

| − | | colspan="2" style="background:#8FBC9F; text-align:center; padding:1px; border-bottom:1px #8FBC9F solid;" |

| |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Reliability of Electronic Products </h2>

| |

| − | |-

| |

| − | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> |

| |

| − |

| |

| − | The rapid developments in electronics, especially in the last decade, have elevated the importance of electronics reliability. Conventionally used accelerated reliability tests have lost their significance; time consuming and expensive feature of these tests is against the demands of today's very rapid electronic product cycles. In this study, we propose less costly, yet accurate, reliability prediction techniques using field return data, new accelerated test methodologies, and physics of failure based simulations. We cooperate with one of the Europe’s largest household appliance companies [http://www.arcelik.com.tr/default.aspx?lang=en-US Arçelik A.Ş.].

| |

| − |

| |

| − | [[Image:Research-3.png|center|none|800px|link=]]

| |

| − |

| |

| − | <h3>

| |

| − | Reliability Analysis and Prediction with Field Data</h3>

| |

| − |

| |

| − | We propose an '''accurate reliability prediction''' model for high-volume electronic products throughout their warranty periods by using field return data. Our model is constructed on a Weibull-exponential hazard rate scheme by using the '''proposed change point detection method''' based on backward and forward data analysis. Our prediction model can make a '''36-month''' (full warranty) reliability prediction of an electronic board with using its field data as short as '''3 months'''.

| |

| − |

| |

| − | <h3>

| |

| − | Degradation Processes in Varistors</h3>

| |

| − |

| |

| − | We investigate different degradation mechanisms of ZnO varistors. We propose a model showing how the varistor voltage Vv changes by time for different stress levels. For this purpose, accelerated degradation tests are applied for different AC current levels; then voltage values are measured. Different from the common practice in the literature that considers a degradation with only decreasing Vv values, we demonstrate '''either an increasing or a decreasing trend in the Vv parameter'''.

| |

| − |

| |

| − | <h3>

| |

| − | Calibrated Accelerated Life Testing</h3>

| |

| − |

| |

| − | Dramatic decrease in failure rates for electronic products makes conventional accelerated life tests ('''ALT''') extremely time consuming and costly. Recently proposed calibrated accelerated life tests ('''CALT''') aim to use fewer samples than those used in ALT. We thoroughly compare ALT and CALT by considering the effects of failure rate, acceleration factor, and stress level on the required test time.

| |

| − |

| |

| − | <!-- YAYIN -->

| |

| − | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;"

| |

| − | | class="MainPageBG" style="width:50%; border:0px solid #D8BFD8; vertical-align:top; color:#000;" |

| |

| − | {| id="mp-left" style="width:100%; vertical-align:top;"

| |

| − |

| |

| − | |

| |

| − |

| |

| − | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;"

| |

| − |

| |

| − | |- valign=top

| |

| − | | width="696" |'''Selected Publications'''

| |

| − | |}

| |

| − |

| |

| − | {| style="border:1px solid #abd5f5; background:#f1f5fc;"

| |

| − |

| |

| − | |

| |

| − | {|

| |

| − | |- valign=top

| |

| − | | width="100" |'''title''':

| |

| − | | width="450"|[[Media:Altun_Comert_A_Change-Point_based_Reliability_Prediction_Model_using_Field_Return_Data.pdf| A Change-Point based Reliability Prediction Model using Field Return Data]]

| |

| − | |- valign="top"

| |

| − | | '''authors''':

| |

| − | | [[Mustafa Altun]] and Vehbi Comert

| |

| − | |- valign=top

| |

| − | | '''accepted in''':

| |

| − | | [http://www.journals.elsevier.com/reliability-engineering-and-system-safety Reliability Engineering and System Safety], 2016.

| |

| − | |- valign=top

| |

| − | | '''presented at''':

| |

| − | | [http://rams.org/ Reliability and Maintainability Symposium (RAMS)],<br> Palm Harbor, USA, 2015.

| |

| − | |}

| |

| − |

| |

| − | | align=center width="70" |

| |

| − | <span class="plainlinks">

| |

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/1/16/Altun_Comert_A_Change-Point_based_Reliability_Prediction_Model_using_Field_Return_Data.pdf]]</span>

| |

| − | <br>

| |

| − | [[Media:Altun_Comert_A_Change-Point_based_Reliability_Prediction_Model_using_Field_Return_Data.pdf | Paper]]

| |

| − | | align="center" width="70" |

| |

| − | <span class="plainlinks">

| |

| − |

| |

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/a/a7/Comert_Altun_Nadar_Erturk_Warranty_Forecasting_of_Electronic_Boards_using_Short-term_Field_Data.pptx]]

| |

| − | </span>

| |

| − | <br> [http://www.ecc.itu.edu.tr/images/a/a7/Comert_Altun_Nadar_Erturk_Warranty_Forecasting_of_Electronic_Boards_using_Short-term_Field_Data.pptx Slides]

| |

| − | |}

| |

| − |

| |

| − | {| style="border:1px solid #abd5f5; background:#f1f5fc;"

| |

| − |

| |

| − | |

| |

| − | {|

| |

| − | |- valign=top

| |

| − | | width="100" |'''title''':

| |

| − | | width="450"|[[Media: Yadavari_Altun_Distinct_Degradation_Processes_in_ZnO_varistors.pdf | Distinct Degradation Processes in ZnO Varistors: Reliability Analysis and Modeling with Accelerated AC Tests]]

| |

| − | |- valign="top"

| |

| − | | '''authors''':

| |

| − | | Hadi Yadavari and [[Mustafa Altun]]

| |

| − | |- valign=top

| |

| − | | '''accepted in''':

| |

| − | | [http://journals.tubitak.gov.tr/elektrik/index.htm;jsessionid=848207EBE52EFE10C78B78C76A0FEAD9 Turkish Journal of Electrical Engineering and Computer Sciences], 2016.

| |

| − | |- valign="top"

| |

| − | | '''presented at''':

| |

| − | | [http://esrel2015.ethz.ch/ European Safety and Reliability Conference (ESREL)],<br> Zurich, Switzerland, 2015.

| |

| − | |}

| |

| − | | align=center width="70" |

| |

| − | <span class="plainlinks">

| |

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/d/dd/Yadavari_Altun_Distinct_Degradation_Processes_in_ZnO_varistors.pdf]]</span>

| |

| − | <br>

| |

| − | [[Media:Yadavari_Altun_Distinct_Degradation_Processes_in_ZnO_varistors.pdf | Paper]]

| |

| − | | align="center" width="70" |

| |

| − | <span class="plainlinks">

| |

| − |

| |

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/d/de/Yadavari_EtAl_Effects_of_ZnO_Varistor_Degradation_on_the_Overvoltage_Protection_Mechanism_of_Electronic_Boards.pptx]]

| |

| − | </span>

| |

| − | <br> [http://www.ecc.itu.edu.tr/images/d/de/Yadavari_EtAl_Effects_of_ZnO_Varistor_Degradation_on_the_Overvoltage_Protection_Mechanism_of_Electronic_Boards.pptx Slides]

| |

| − | |}

| |

| − |

| |

| − | {| style="border:1px solid #abd5f5; background:#f1f5fc;"

| |

| − |

| |

| − | |

| |

| − | {|

| |

| − | |- valign=top

| |

| − | | width="100" |'''title''':

| |

| − | | width="450"|[[Media:Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pdf | Extensive Investigation of Calibrated Accelerated Life Testing (CALT) in Comparison with Classical Accelerated Life Testing (ALT)]]

| |

| − | |- valign="top"

| |

| − | | '''authors''':

| |

| − | | Burak Sal and [[Mustafa Altun]]

| |

| − | |- valign="top"

| |

| − | | '''presented at''':

| |

| − | | [http://esrel2015.ethz.ch/ European Safety and Reliability Conference (ESREL)],<br> Zurich, Switzerland, 2015.

| |

| − | |}

| |

| − | | align=center width="70" |

| |

| − | <span class="plainlinks">

| |

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/0/07/Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pdf]]</span>

| |

| − | <br>

| |

| − | [[Media:Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pdf | Paper]]

| |

| − | | align="center" width="70" |

| |

| − | <span class="plainlinks">

| |

| − |

| |

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/a/a8/Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pptx]]

| |

| − | </span>

| |

| − | <br> [http://www.ecc.itu.edu.tr/images/a/a8/Sal_Altun_Extensive_Investigation_of_CALT_in_Comparison_with_ALT.pptx Slides]

| |

| − | |}

| |

| − | |}

| |

| − | | style="border:1px solid transparent;" |

| |

| − | <!-- PROJE -->

| |

| − | | class="MainPageBG" style="width:50%; border:0px solid #A9A9A9; vertical-align:top;"|

| |

| − | {| id="mp-right" style="width:100%; vertical-align:top;"

| |

| − | |

| |

| − |

| |

| − | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;"

| |

| − |

| |

| − | |- valign=top

| |

| − | | width="696" |'''Funding Projects'''

| |

| − | |}

| |

| − | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;"

| |

| − |

| |

| − | |

| |

| − | {|

| |

| − | |- valign=top

| |

| − | | width="140" |'''title''':

| |

| − | | width="558"|An Accurate Reliability Methodology for Appliance Electronic Cards

| |

| − | |- valign="top"

| |

| − | | '''agency & program''':

| |

| − | | [http://www.tubitak.gov.tr/tr/destekler/akademik/ulusal-destek-programlari/icerik-1505-universite-sanayi-isbirligi-destek-programi TUBITAK University-Industry Collaboration Grant Program (1505)]

| |

| − | |- valign="top"

| |

| − | | '''budget''':

| |

| − | | 211.800 TL

| |

| − | |- valign="top"

| |

| − | | '''duration''':

| |

| − | | 2013-2015, ''completed''

| |

| − | |}

| |

| − |

| |

| − | |}

| |

| − | {| style="margin-left: auto; margin-right: 0px; border:1px solid #abd5f5; background:#f1f5fc;"

| |

| − |

| |

| − | |

| |

| − | {|

| |

| − | |- valign="top"

| |

| − | | width="140" |'''title''':

| |

| − | | width="558"|Gate Oxide Breakdown Failure Mechanism of CMOS Transistors

| |

| − | |- valign="top"

| |

| − | | '''agency & program''':

| |

| − | | [http://www.tubitak.gov.tr/tr/burslar/lisans/burs-programlari/icerik-2209-b-sanayi-odakli-lisans-bitirme-tezi-destekleme-programi TUBITAK Industry Oriented Senior Project Support Program (2241/A)]

| |

| − | |- valign="top"

| |

| − | | '''duration''':

| |

| − | | 2013-2014, ''completed''

| |

| − | |}

| |

| − |

| |

| − | |}

| |

| − |

| |

| − | |}

| |

| − | |}

| |

| − | |}

| |

| − |

| |

| − | <!-- ANALOG -->

| |

| − |

| |

| − |

| |

| − | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;"

| |

| − | |-

| |

| − | | colspan="2" style="background:#8FBC8F; text-align:center; padding:1px; border-bottom:1px #8FBC8F solid;" |

| |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Analog Circuit Design </h2>

| |

| − | |-

| |

| − | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> |

| |

| − |

| |

| − | <h3>

| |

| − | Positive Feedback</h3>

| |

| − | The conventional wisdom is that analog circuits should not include positive feedback loops. As controversial as it seems, we have successfully used '''positive feedback''' for impedance improvement in a current amplifier. With adding few transistors we have achieved very low input resistance values. Additionally, we have proposed a new fully-differential current amplifier and tested it in a filter application.

| |

| − |

| |

| − | <!-- YAYIN -->

| |

| − | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;"

| |

| − | | class="MainPageBG" style="width:50%; border:0px solid #D8BFD8; vertical-align:top; color:#000;" |

| |

| − | {| id="mp-left" style="width:100%; vertical-align:top;"

| |

| − |

| |

| − | |

| |

| − |

| |

| − | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;"

| |

| − |

| |

| − | |- valign=top

| |

| − | | width="696" |'''Selected Publications'''

| |

| − | |}

| |

| − | {| style="border:1px solid #abd5f5; background:#f1f5fc;"

| |

| − |

| |

| − | |

| |

| − | {|

| |

| − | |- valign=top

| |

| − | | width="100" |'''title''':

| |

| − | | width="450"|[[Media:Altun_Kuntman_Design_of_a_Fully_Differential_Current_Mode_Operational_Amplifier_with_its_Filter_Applications.pdf | Design of a Fully Differential Current Mode Operational Amplifier with its Filter Applications]]

| |

| − | |- valign="top"

| |

| − | | '''authors''':

| |

| − | | [[Mustafa Altun]] and [http://web.itu.edu.tr/~kuntman/ Hakan Kuntman]

| |

| − | |- valign="top"

| |

| − | | '''appeared in''':

| |

| − | | [http://www.sciencedirect.com/science/journal/14348411 AEU International Journal of Electronics and Communications], <br>Vol. 62, Issue 3, pp. 39–44, 2008.

| |

| − | |- valign="top"

| |

| − | | '''presented at''':

| |

| − | | [http://www.glsvlsi.org/ ACM Great Lakes Symposium on VLSI (GLSVLSI)], Stresa, Italy, 2007.

| |

| − | |}

| |

| − | | align=center width="70" |

| |

| − | <span class="plainlinks">

| |

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/e/e5/Altun_Kuntman_Design_of_a_Fully_Differential_Current_Mode_Operational_Amplifier_with_its_Filter_Applications.pdf]]</span>

| |

| − | <br>

| |

| − | [[Media:Altun_Kuntman_Design_of_a_Fully_Differential_Current_Mode_Operational_Amplifier_with_its_Filter_Applications.pdf | Paper]]

| |

| − | | align="center" width="70" |

| |

| − | <span class="plainlinks">

| |

| − |

| |

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/7/77/Altun_Kuntman_A_Wideband_CMOS_Current-Mode_Operational_Amplifier_and_Its_Use_for_Band-Pass_Filter_Realization.ppt]]

| |

| − | </span>

| |

| − | <br> [http://www.ecc.itu.edu.tr/images/7/77/Altun_Kuntman_A_Wideband_CMOS_Current-Mode_Operational_Amplifier_and_Its_Use_for_Band-Pass_Filter_Realization.ppt Slides]

| |

| − | |}

| |

| − |

| |

| − | |}

| |

| − | | style="border:1px solid transparent;" |

| |

| − | <!-- PROJE -->

| |

| − |

| |

| − | |}

| |

| − | |}

| |

| − |

| |

| − | <!-- MATHEMATICS -->

| |

| − |

| |

| − |

| |

| − | {| id=portal cellspacing="0" cellpadding="0" width=100% style="border:1px solid #B8C7D9; padding:0px;"

| |

| − | |-

| |

| − | | colspan="2" style="background:#8FBC7F; text-align:center; padding:1px; border-bottom:1px #8FBC7F solid;" |

| |

| − | <h2 style="margin:.1em; border-bottom:1px; font-size:140%; font-weight:bold;"> Discrete Mathematics </h2>

| |

| − | |-

| |

| − | | valign="top" style="padding:8px 8px 0px 8px; background:#f5fffa;" <!--H210 S4 V100--> |

| |

| − |

| |

| − | <h3>

| |

| − | Self Duality Problem</h3>

| |

| − |

| |

| − | The problem of testing whether a monotone Boolean function in irredundant disjuntive normal form (IDNF) is self-dual is one of few problems in circuit/time complexity whose precise tractability status is '''unknown'''. We have focused on this '''famous problem'''. We have shown that monotone self-dual Boolean functions in IDNF do not have more variables than disjuncts. We have proposed an algorithm to test whether a monotone Boolean function in IDNF with ''n'' variables and ''n'' disjuncts is self-dual. The algorithm runs in O(n^3) time.

| |

| − | <!-- YAYIN -->

| |

| − | {| id="mp-upper" style="width: 100%; margin:4px 0 0 0; background:none; border-spacing: 0px;"

| |

| − | | class="MainPageBG" style="width:50%; border:0px solid #D8BFD8; vertical-align:top; color:#000;" |

| |

| − | {| id="mp-left" style="width:100%; vertical-align:top;"

| |

| − |

| |

| − | |

| |

| − |

| |

| − | {| style="border:1px solid #abd5f5; background:#d0e5f5; padding:0.2em 0.5em; font-weight:bold;"

| |

| − |

| |

| − | |- valign=top

| |

| − | | width="696" |'''Selected Publications'''

| |

| − | |}

| |

| − | {| style="border:1px solid #abd5f5; background:#f1f5fc;"

| |

| − |

| |

| − | |

| |

| − | {|

| |

| − | |- valign=top

| |

| − | | width="100" |'''title''':

| |

| − | | width="450"|[[Media:Altun_Riedel_A_Study_on_Monotone_Self_Dual_Boolean_Functions.pdf | A Study on Monotone Self-dual Boolean Functions]]

| |

| − | |- valign="top"

| |

| − | | '''authors''':

| |

| − | | [[Mustafa Altun]] and [http://cadbio.com/wiki/index.php/Marc_Riedel Marc Riedel]

| |

| − | |- valign="top"

| |

| − | | '''appeared in''':

| |

| − | | [http://www.springer.com/mathematics/applications/journal/10255 Acta Mathematicae Applicatae Sinica - English Series], <br>Vol. 32, 2016.

| |

| − | |}

| |

| − | | align=center width="70" |

| |

| − | <span class="plainlinks">

| |

| − | [[File:PDF.png|65px|link=http://www.ecc.itu.edu.tr/images/5/53/Altun_Riedel_A_Study_on_Monotone_Self_Dual_Boolean_Functions.pdf]]</span>

| |

| − | <br>

| |

| − | [[Media:Altun_Riedel_A_Study_on_Monotone_Self_Dual_Boolean_Functions.pdf | Paper]]

| |

| − | | align="center" width="70" |

| |

| − | <span class="plainlinks">

| |

| − |

| |

| − | [[File:PPT.jpg|60px|link=http://www.ecc.itu.edu.tr/images/1/18/Altun_Riedel_A_Study_on_Monotone_Self_Dual_Boolean_Functions.ppt]]

| |

| − | </span>

| |

| − | <br> [http://www.ecc.itu.edu.tr/images/1/18/Altun_Riedel_A_Study_on_Monotone_Self_Dual_Boolean_Functions.ppt Slides]

| |

| − | |}

| |

| − |

| |

| − | |}

| |

| − | | style="border:1px solid transparent;" |

| |

| − | <!-- PROJE -->

| |

| − |

| |

| | |} | | |} |

| | |} | | |} |

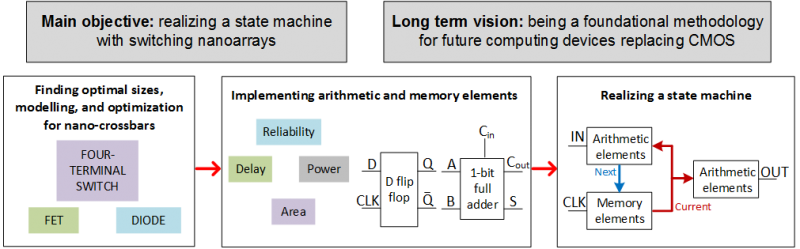

We aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer. Our objectives are 1) synthesizing Boolean functions with area optimization; 2) achieving fault tolerance; 3) performing performance optimization by considering area, delay, power, and accuracy; 4) implementing arithmetic and memory elements; and 5) realizing a synchronous state machine.