Main Page

| Line 103: | Line 103: | ||

* We present our work "''Computing with Nano-Crossbar Arrays: Logic Synthesis and Fault Tolerance''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2017]. | * We present our work "''Computing with Nano-Crossbar Arrays: Logic Synthesis and Fault Tolerance''" in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2017]. | ||

| − | * Our paper is accepted in a leading journal [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=43 TCAD]. | + | * Our paper is accepted in a leading journal in design automation [http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=43 IEEE TCAD]. |

* We give an invited talk "''EU H2020 Success Story''" in [http://msca-association.teamwork.fr/en/programme H2020 MSCA 2016 Istanbul Training & Info Event]. | * We give an invited talk "''EU H2020 Success Story''" in [http://msca-association.teamwork.fr/en/programme H2020 MSCA 2016 Istanbul Training & Info Event]. | ||

| Line 115: | Line 115: | ||

* We present and exhibit our ''EU H2020 project NANOxCOMP'' in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2016] with over 1000 attendees from academia and industry. | * We present and exhibit our ''EU H2020 project NANOxCOMP'' in a premier conference on electronic design automation [http://www.date-conference.com/ DATE 2016] with over 1000 attendees from academia and industry. | ||

| + | * We publish a book chapter "''Computing with Emerging Nanotechnologies''" in a book [https://link.springer.com/book/10.1007/978-3-319-25340-4 Low-Dimensional and Nanostructured Materials and Devices]. | ||

[[Image:Funding-3.png|center|none|450px|link=http://www.ecc.itu.edu.tr/index.php?title=Projects]] | [[Image:Funding-3.png|center|none|450px|link=http://www.ecc.itu.edu.tr/index.php?title=Projects]] | ||

Revision as of 22:00, 10 April 2017

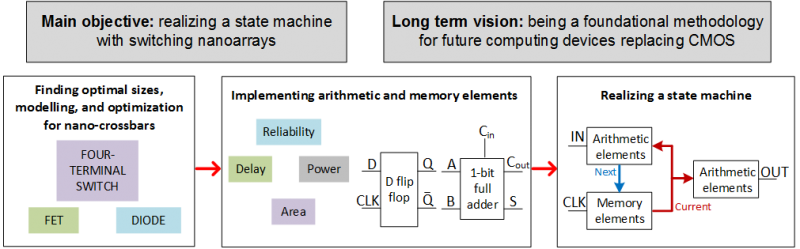

Welcome to the NANOxCOMP Project | |

|

Nano-crossbar arrays have emerged as a strong candidate technology to replace CMOS in near future. They are regular and dense structures, and fabricated by exploiting self-assembly as opposed to purely using lithography based conventional and relatively costly CMOS fabrication techniques. Currently, nano-crossbar arrays are fabricated such that each crosspoint can be used as a conventional electronic component such as a diode, a FET, or a switch. This is a unique opportunity that allows us to integrate well developed conventional circuit design techniques into nano-crossbar arrays. Motivated by this, we aim to develop a complete synthesis and performance optimization methodology for switching nano-crossbar arrays that leads to the design and construction of an emerging nanocomputer.

| |

|

|

|